Product Summary

The 74LVC14APW is a high-performance, low power, low-voltage Si-gate CMOS device and superior to most advanced CMOS compatible TTL families. Inputs can be driven from either 3.3 V or 5 V devices. This feature allows the use of these devices as translators in a mixed 3.3 V/5 V environment. The 74LVC14APW provides six inverting buffers with Schmitt-trigger action. It is capable of transforming slowly changing input signals into sharply defined, jitter-free output signals.

Parametrics

Absolute maximum ratings: (1)VCC, DC supply voltage: –0.5 to +6.5 V; (2)IIK, DC input diode current at VI< 0: –50 mA; (3)VI DC, input voltage: –0.5 to +6.5 V; (4)IOK, DC output diode current at VO>VCC or VO< 0: ±50 mA; (5)VI/O: DC output voltage; output HIGH or LOW: 2 –0.5 to VCC +0.5V; DC input voltage; output 3-State: –0.5 to 6.5v; (6)IO, DC output source or sink current at VO = 0 to VCC: ±50 mA; (7)IGND, ICC, DC VCC or GND current: ±100 mA; (8)Tstg, Storage temperature range: –65 to +150 ℃; (9)PTOT: plastic mini-pack (SO) above +70℃ derate linearly with 8 mW/K: 500mW; plastic shrink mini-pack (SSOP and TSSOP) above +60℃ derate linearly with 5.5 mW/K: 500mW.

Features

Features: (1)Wide supply voltage range of: 1.2 V to 3.6 V; (2)In accordance with JEDEC standard no. 8-1A; (3)Inputs accept voltages up to 5.5 V; (4)CMOS low power consumption; (5)Direct interface with TTL levels.

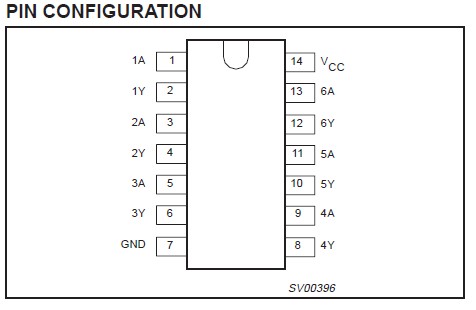

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74LVC14APW |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||

|

74LVC14APW,112 |

NXP Semiconductors |

Inverters HEX INVERTER SCHMITT TRGGR |

Data Sheet |

|

|

||||||||||||||||

|

74LVC14APW,118 |

NXP Semiconductors |

Inverters HEX INV SCHMITT TRIG |

Data Sheet |

|

|

||||||||||||||||

|

74LVC14APW/S999,11 |

|

IC HEX SCHMITT INVERTER 14TSSOP |

Data Sheet |

|

|

||||||||||||||||

(Hong Kong)

(Hong Kong)